Commenting to get notified when answers to the questions posed by @gohan2021 are posted.

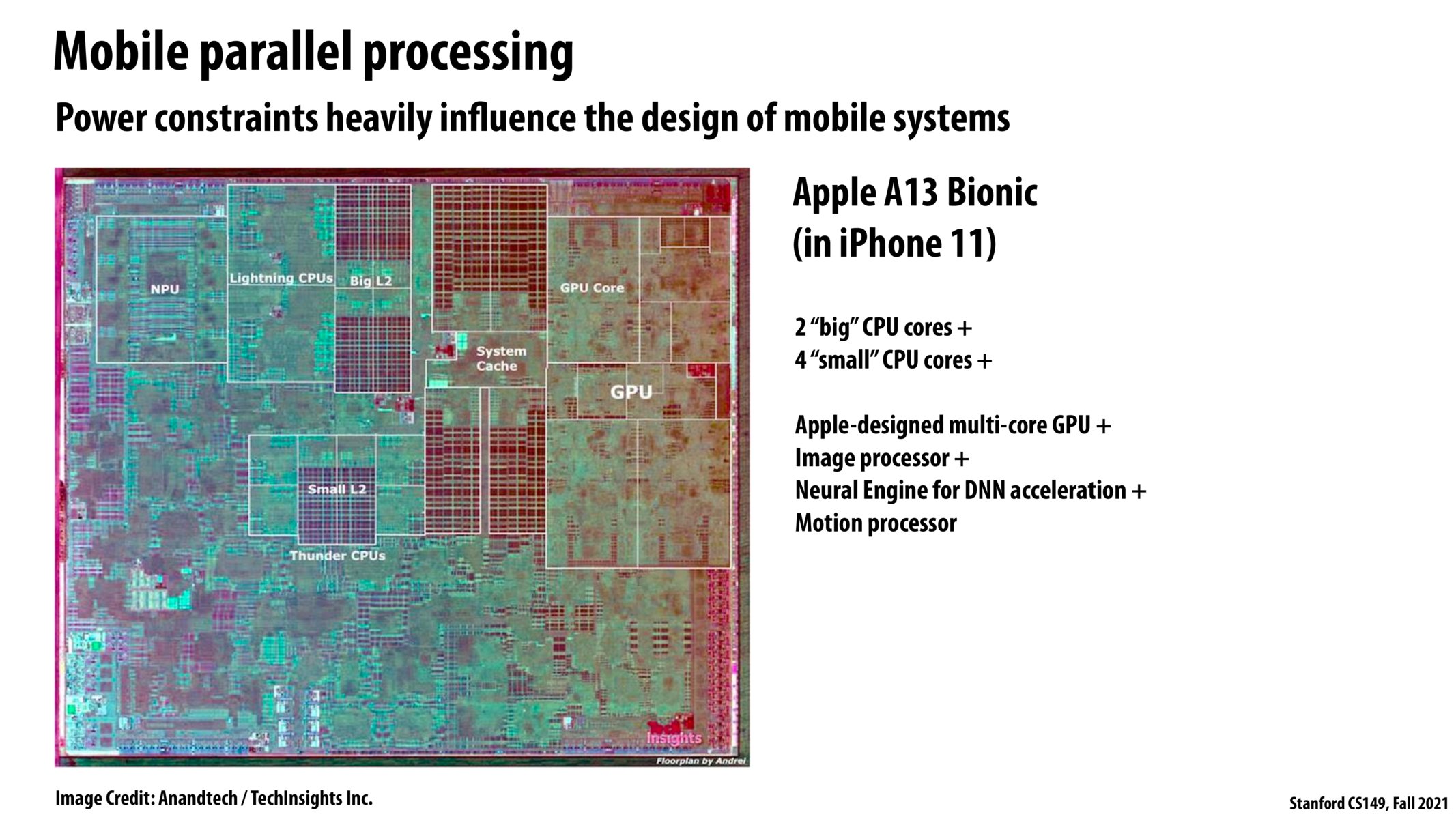

I wonder how engineers at Apple and Intel along with other companies designing "big little" CPUs test which combination of big and little cores equals the performance numbers they are looking for. For example 3 big and 2 little may have the same overall performance has 2 big 4 little however the chip draws the same power with fewer total cores. Would there be some monolithic chip put inside one of these phones that have the ability of enabling/disabling cores to the engineers' heart's content to find this golden ratio?

What is the intuition of having more efficiency cores than high performance cores? Specifically I'm curious about what the factors are when designing the number of "small" cores. More parallelization in less performance-demanding applications seem counterintuitive.

Please log in to leave a comment.

increasing the number of pipeline stages increases the clock frequency which increases the power consumption per instruction. So could I say that mobile processor and GPUs do not implement super-scalar architecture and deep pipeline stages, or implement simplified version of it to reduce power consumption?

Also, does the specialized hardware architecture also includes ILP or Pipelining hardware features?